# 2.7V to 5.5V, Serial Input, Voltage Output, 16-Bit DAC

#### PRODUCT DESCRIPTION

The MS5543 is a single-channel, 16-bit, serial input and voltage output digital-to-analog converter(DAC). It operates from single power supply with 2.7V to 5.5V, and the output range is from 0V to VREF. Within the output range, the monotonicity is ensured. And it could provide 1LSB INL accuracy at 14-bit in the temperature range from -40°C to +85°C. The MS5543 provides unbuffered output and has many features, including short setup time, low power dissipation and low offset error. In addition, due to the low noise and low glitch characteristics, the MS5543 is suitable for several terminal systems.

## **FEATURES**

- 14-bit Effective Resolution

- 3V or 5V Single Power Supply

- Low Power Dissipation: 0.825mW

- Setup Time: 1.2µs

- Power-on Reset Value: Mid-Code

- Unbuffered Voltage Output, Directly Drive 60kΩ Load

- Low Glitch: 1.1nV-s

- Compatible with SPI/QSPI/MICROWIRE and DSP Interface Standards

#### **APPLICATIONS**

- Precision Measurement Device

- **Automatic Test Device**

- **Data Acquisition System**

- **Industrial Process Control**

#### **PRODUCT SPECIFICATION**

| Part Number | Package | Marking |

|-------------|---------|---------|

| MS5543      | SOP14   | MS5543  |

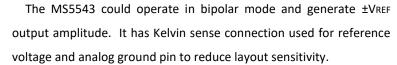

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin | Name          | Туре | Description                                                                                                            |

|-----|---------------|------|------------------------------------------------------------------------------------------------------------------------|

| 1   | RFB           | 0    | Resistor Feedback Pin. In bipolar mode, connect with external amplifier output                                         |

| 2   | VOUT          | 0    | DAC Analog Output Voltage                                                                                              |

| 3   | AGNDF         | -    | Analog Reference Ground                                                                                                |

| 4   | AGNDS         | ı    | Analog Reference Ground                                                                                                |

| 5   | REFS          | I    | DAC Reference Input Voltage (Sense). Connect with external 2.5V and the voltage range is form 2V to VDD                |

| 6   | REFF          | I    | DAC Reference Input Voltage (Force). Connect with external 2.5V and the voltage range is form 2V to VDD                |

| 7   | <del>CS</del> | I    | Logic Input Signal. Chip select is used for input control of serial data                                               |

| 8   | SCLK          | I    | Clock Input. Data enters into register at the rising edge                                                              |

| 9   | NC            | -    | Not Connection                                                                                                         |

| 10  | DIN           | 1    | Serial Data Input. Support 16-bit data and data enters into register at the SCLK rising edge                           |

| 11  | LDAC          | ı    | When input is low level, DAC register is simultaneously updated with the content of serial register data               |

| 12  | DGND          | 1    | Digital Reference Ground                                                                                               |

| 13  | INV           | 0    | Connect to DAC Internal Scaling Resistor. In bipolar mode, connect with inverting input terminal of external amplifier |

| 14  | VDD           | -    | Power Supply                                                                                                           |

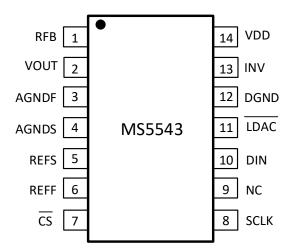

# **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

Any exceeding absolute maximum rating application causes permanent damage to device. Because long-time absolute operation state affects device reliability. Absolute ratings just conclude from a series of extreme tests. It doesn't represent chip can operate normally in these extreme conditions.

DGND=AGND=0V. All voltage values are all relative to 0V.

| Parameter                          | Symbol | Ratings     | Unit |

|------------------------------------|--------|-------------|------|

| Power Supply                       | VDD    | -0.3 ~ +6.0 | V    |

| Input Current                      | lin    | ±10         | mA   |

| Operating Temperature <sup>1</sup> | Та     | -40 ~ +85   | °C   |

| Storage Temperature <sup>1</sup>   | Tstg   | -65 ~ +150  | °C   |

| ESD                                | НВМ    | >±3k        | V    |

Note 1: All temperature conditions are Ta= 25°C, except operating temperature and storage temperature.

## **RECOMMENDED OPERATING CONDITIONS**

|                   |        | Range |     |     |      |

|-------------------|--------|-------|-----|-----|------|

| Parameter         | Symbol | Min   | Тур | Max | Unit |

| Power Supply      | Vdd    | 2.7   | 5   | 5.5 | V    |

| Reference Voltage | VREF   | 2     | 2.5 | Vdd | V    |

# **ELECTRICAL CHARACTERISTICS**

$\label{eq:dd} V \texttt{DD=2.7V} \sim 5.5 \texttt{V}, \, \mathsf{VREF=2V} \sim \mathsf{VDD}, \, \mathsf{AGND=DGND=0V}, \, \mathsf{Ta=Tmin} \sim \mathsf{Tmax}$

Note: Unless otherwise noted,  $T_A = 25^{\circ}C \pm 2^{\circ}C$ .

| Parameter                                           | Condition               | Min   | Тур   | Max       | Unit        |

|-----------------------------------------------------|-------------------------|-------|-------|-----------|-------------|

|                                                     | Static Characteristics  |       |       |           |             |

| Resolution                                          |                         | 14    |       |           | bits        |

| Integral Nonlinearity (INL)                         | VREF=2.048V,VDD=5V,     |       | ±6.5  | ±10.5     | LSB         |

| Differential Nonlinearity (DNL)                     | Ta=25°C                 |       | ±4    | ±5        | LSB         |

| Gain Error                                          | Ta=25°C                 |       | ±2    | ±5        | LSB         |

| Gain Error Temperature Coefficient                  |                         |       | ±0.1  |           | ppm/°C      |

| Unipolar Zero Code Error                            | Ta=25°C                 |       | ±2    | ±2.5      | LSB         |

| Unipolar Zero Code Error<br>Temperature Coefficient |                         |       | ±0.05 |           | ppm/°C      |

| Bipolar Zero Offset Error                           | Ta=25°C                 |       | ±2    | ±5        | LSB         |

| Bipolar Zero Temperature Coefficient                |                         |       | ±0.2  |           | ppm/°C      |

| Bipolar Zero Code Offset Error                      | Ta=25°C                 |       | ±2    | ±5        | LSB         |

| Bipolar Gain Error                                  | Ta=25°C                 |       | ±2    | ±5        | LSB         |

| Bipolar Gain Temperature Coefficien                 | t                       |       | ±0.1  |           | ppm/°C      |

|                                                     | Output Characteristics  |       |       |           |             |

| Output Voltage                                      | Bipolar Mode            | -VREF |       | VREF-1LSB | V           |

| Setup Time, Output Voltage                          | CL=10pF                 |       | 1.2   |           | μs          |

| Conversion Rate                                     | CL=10pF,0%-63%          |       | 4     |           | V/µs        |

| Digital-to-Analog Glitch Impulse                    | 1LSB                    |       | 18    |           | nV-sec      |

| Digital Feedthrough                                 | VREF=2.048V             |       | 0.2   |           | nV-sec      |

| Output Noise Density                                | DAC Code=0×8400, f=1kHz |       | 11.8  |           | nV ∕<br>√Hz |

| Output Noise Voltage                                | f=0.1Hz to 10Hz         |       | 0.134 |           | μVр-р       |

| Power Supply Rejection Ratio                        | ΔVDD±10%                |       |       | ±1.0      | LSB         |

|                                                     | DAC Reference Input     |       |       |           |             |

| Reference Input Range                               |                         | 2.0   |       | VDD       | V           |

| Reference Input Impedance                           | Bipolar Mode            | 72    |       |           | kΩ          |

| Parameter          | Condition          | Min | Тур   | Max   | Unit |

|--------------------|--------------------|-----|-------|-------|------|

|                    | Logic Inpu         | t   |       |       |      |

| Input Current      |                    |     |       | ±1    | μΑ   |

| Input Low Voltage  |                    |     |       | 0.8   | V    |

| Input High Voltage |                    | 2.4 |       |       | V    |

| Input Capacitance  |                    |     |       | 10    | pF   |

| Hysteresis Voltage |                    |     | 0.15  |       | V    |

|                    | Power Supp         | oly |       |       |      |

| Power Supply       |                    | 2.7 |       | 5.5   | V    |

| Current            | Digital input is 0 |     | 165   | 227   | μΑ   |

| Power Dissipation  | Digital input is 0 |     | 0.825 | 1.248 | mW   |

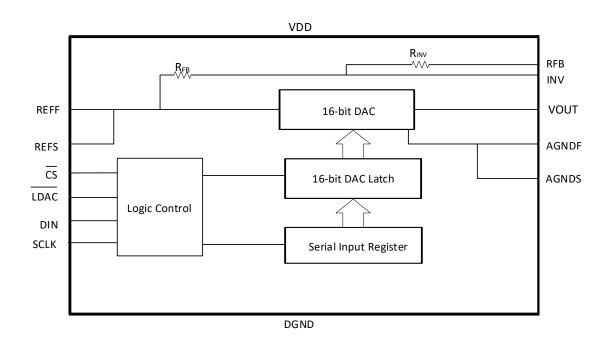

# **CLOCK CHARACTERISTICS**

Unless otherwise noted: Vdd=2.7V  $\sim$  5.5V $\pm$ 10%, Vref=2.048V, Vinh=90% Vdd, Vinl= 10%Vdd, AGND=DGND=0V, -40°C< Ta <+85°C.

| Parameter | Description                      | Value | Unit   |

|-----------|----------------------------------|-------|--------|

| fsclk     | SCLK Cycle Frequency             | 20    | MHz    |

| t1        | SCLK Cycle Time                  | 50    | ns min |

| t2        | SCLK High-level Time             | 25    | ns min |

| t3        | SCLK Low-level Time              | 25    | ns min |

| t4        | Setup Time, CS Low to SCLK High  | 30    | ns min |

| t5        | Setup Time, CS High to SCLK High | 45    | ns min |

| t6        | Hold Time, SCLK High to CS Low   | 45    | ns min |

| t7        | Hold Time, SCLK High to CS High  | 30    | ns min |

| t8        | Data Start Time                  | 20    | ns min |

| t9        | Data Hold Time                   | 10    | ns min |

| t10       | LDAC Pulse Width                 | 60    | ns min |

| t11       | CS High to LDAC Low              | 60    | ns min |

| t12       | Valid Time, CS High              | 60    | ns min |

# **Timing Diagram**

# **TYPICAL CHARACTERISTICS**

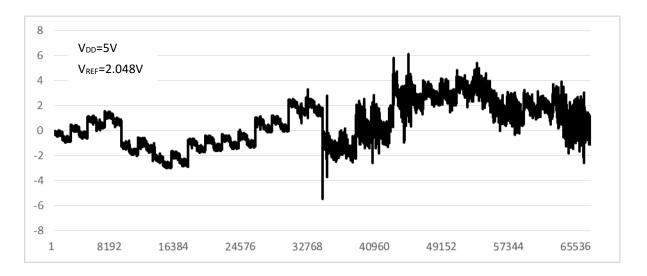

Figure 1. INL VS. Code

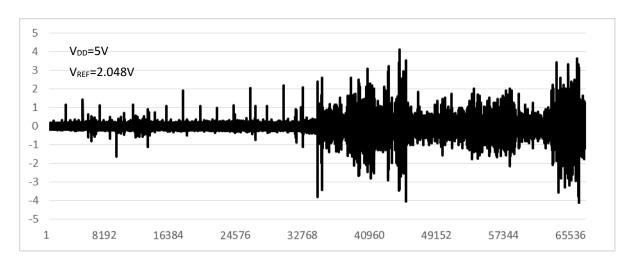

Figure 2. DNL VS. Code

### **OPERATING PRINCIPLE**

The MS5543 is a single-channel, 16-bit, serial input and voltage output DAC, whose operating voltage range is from 2.7V to 5.5V. The typical current consumption is 165µA at 5V power supply. Data is written to the device in 16-bit word format through 3-wire or 4-wire serial interface. In bipolar mode, the MS5543 power-on reset outputs 0. The MS5543 has Kelvin sense connection used for reference voltage and analog ground.

#### **Digital-to-Analog Section**

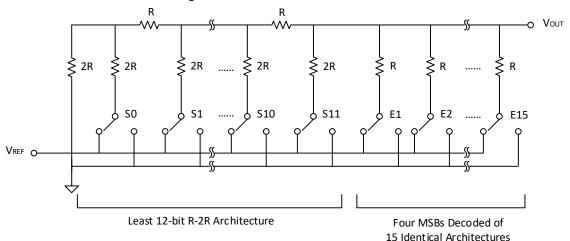

DAC architecture consists of two matched DAC sections. Figure 3 is simplified circuit diagram. The MS5543 implements segment-type DAC architecture. The four MSBs of 16-bit data are decoded to drive 15 switches, E1 to E15. Each switch would connect one of 15 matched resistors to AGND or VREF. Other 12 bits of 16-bit data drive S0 to S11 switches of voltage mode R-2R ladder network.

Figure 3. DAC Architecture

With this DAC configuration, output impedance is irrelevant to code. However, input impedance of reference voltage source is highly relevant to code. Output voltage is related to reference voltage shown in following formula:

$$V_{OUT} = \frac{V_{REF} \times D}{2^N}$$

Where, D is decimal data word loaded to DAC register. N is DAC resolution. For 2.5V reference voltage, above formula could be simplified as follows:

$$V_{OUT} = \frac{2.5 \times D}{65536}$$

Then, Vout is 1.25V when DAC is loaded to mid-scale; Vout is 2.5V when DAC is loaded to full-scale. LSB is VREF /65536.

#### **Serial Interface**

The MS5543 is controlled by multifunctional 3-wire or 4-wire serial interface. It can operate at maximum 20MHz clock frequency and compatible with SPI, QSPI, MICROWIRE and DSP interface standards. The timing diagram is shown as above. Beside 16-bit DAC register, the MS5543 has an independent serial input register. New data could be pre-loaded to the serial input register and not disturb present DAC output voltage.

Input data is frame-transmitted by chip select input  $\overline{CS}$ . When high-to-low transition occurs on  $\overline{CS}$ , data is shifted synchronously at the rising edge of serial clock SCLK, and latched in serial input register. After 16 data bits are all loaded to serial input register, low-to-high transition occurs on  $\overline{CS}$ . If  $\overline{LDAC}$  is in low level, the contents of shift register would be transmitted to DAC register. If  $\overline{LDAC}$  is in high level, the contents only would be transmitted to serial input register. After new values are completely loaded to serial input register, transmit asynchronously to DAC register by making  $\overline{LDAC}$  low. Data is loaded in 16-bit word format and MSB first. Data is loaded only when  $\overline{CS}$  is in low level.

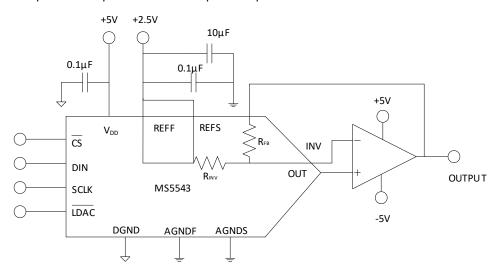

### **Bipolar Output**

For external operation amplifier, the MS5543 could provide bipolar output. The typical circuit is shown in Figure 4. The feedback resistors, RINV and RFB, typical values of  $28k\Omega$ , are connected to input and output terminals of operation amplifier to achieve bipolar output.

Figure 4. Bipolar Output Circuit

If ideal reference voltage source is used, bipolar mode worst-case output voltage can be calculated by the following formula:

$$V_{OUT-BIP} = \frac{\left[ (V_{OUT-UNI} + V_{OS})(2+RD) - V_{REF}(1+RD) \right]}{1 + (2+RD) A}$$

Where, Vout-BIP is the bipolar mode worst-case output voltage. Vout-UNI is the unipolar mode worst-case output voltage. Vos is input offset voltage of external operational amplifier. RD is the matched error of RFB and RINV. A is open-loop gain of operational amplifier.

#### TYPICAL APPLICATION

### **Layout Guide**

In any circuit focusing on accuracy, considering the power and ground loop layout carefully can ensure specified performance. The PCB used by the MS5543 should adopt the design where analog and digital parts are separated and limited to certain field. If several devices demand the connections for analog and digital ground in the MS5543 system, only one point can be connected. Star grounding point is made as close to the device as possible. The MS5543 should have large enough  $10\mu F$  power bypassing capacitor, which is paralleled with  $0.1\mu F$  capacitor of each power. And it should be as close to the package as possible, preferably being faced with the device. The  $10\mu F$  capacitor is tantalum capacitor.  $0.1\mu F$  capacitor should have low effective series resistance(ESR) and low effective series inductance(ESI), such as the ceramic capacitor, which provides low impedance ground path at high-frequency to process transient current caused by internal logic switch.

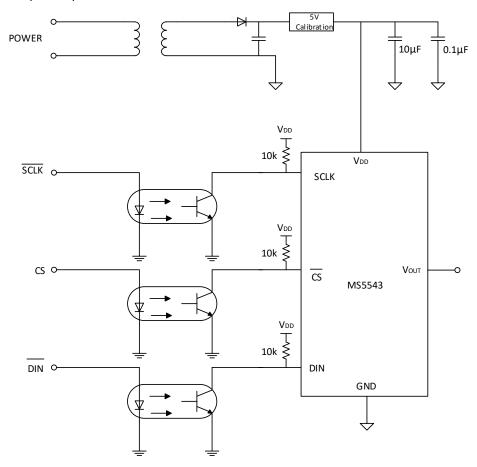

### **Opto-coupler circuit**

The MS5543 is Schmitt-triggered digital input, which makes it receive slow digital transmission. Therefore, it is suitable for industrial application, which may need use opto-coupler to isolate DAC from controller. Figure 5 shows opto-coupler isolation circuit.

Figure 5. Opto-coupler Interface Circuit Diagram

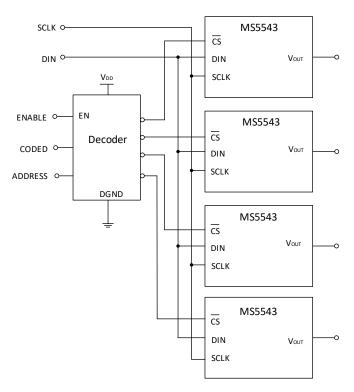

### **Multi-channel Decoding Circuit**

The MS5543 has chip selection pin  $\overline{\text{CS}}$ , which could choose one or several DACs. All devices receive the same serial clock and data, but only one device could receive  $\overline{\text{CS}}$  signal at one time. DAC address is decided by decoder. Digital feedthrough phenomenon exists in digital line. And using burst clock could minimize the impact on analog signal channel. The typical circuit is shown in Figure 6.

Figure 6. Multiple DACs

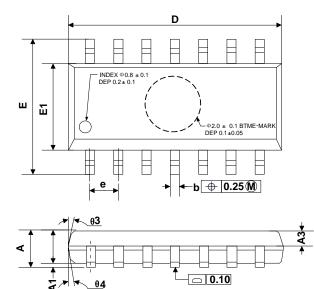

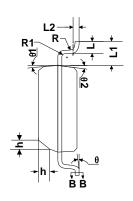

# **PACKAGE OUTLINE DIMENSIONS**

## SOP14

|        |          | Dimensions In Millimeters |      |  |  |

|--------|----------|---------------------------|------|--|--|

| Symbol | Min      | Тур                       | Max  |  |  |

| А      | 1.35     |                           | 1.75 |  |  |

| A1     | 0.10     |                           | 0.25 |  |  |

| A2     | 1.25     |                           | 1.65 |  |  |

| A3     | 0.55     |                           | 0.75 |  |  |

| D      | 8.53     |                           | 8.73 |  |  |

| E      | 5.80     |                           | 6.20 |  |  |

| E1     | 3.80     |                           | 4.00 |  |  |

| е      | 1.27 BSC |                           |      |  |  |

| L      | 0.45     |                           | 0.80 |  |  |

| L1     | 1.04 REF |                           |      |  |  |

| L2     |          | 0.25 BSC                  |      |  |  |

| R      | 0.07     |                           |      |  |  |

| R1     | 0.07     |                           |      |  |  |

| h      | 0.30     |                           | 0.50 |  |  |

| θ      | 0°       |                           | 8°   |  |  |

| θ1     | 6°       | 8°                        | 10°  |  |  |

| θ2     | 6°       | 8°                        | 10°  |  |  |

| θ3     | 5°       | 7°                        | 9°   |  |  |

| θ4     | 5°       | 7°                        | 9°   |  |  |

## **MARKING and PACKAGING SPECIFICATIONS**

## 1. Marking Drawing Description

Product Name: MS5543

Product Code: XXXXXXX

## 2. Marking Drawing Demand

Laser printing, contents in the middle, font type Arial.

## 3. Packaging Specification

| Device | Package | Piece/Reel | Reel/Box | Piece/Box | Box/Carton | Piece/Carton |

|--------|---------|------------|----------|-----------|------------|--------------|

| MS5543 | SOP14   | 2500       | 1        | 2500      | 8          | 20000        |

#### **STATEMENT**

- All Revision Rights of Datasheets Reserved for Ruimeng. Don't release additional notice.

Customer should get latest version information and verify the integrity before placing order.

- When using Ruimeng products to design and produce, purchaser has the responsibility to observe safety standard and adopt corresponding precautions, in order to avoid personal injury and property loss caused by potential failure risk.

- The process of improving product is endless. And our company would sincerely provide more excellent product for customer.

## MOS CIRCUIT OPERATION PRECAUTIONS

Static electricity can be generated in many places. The following precautions can be taken to effectively prevent the damage of MOS circuit caused by electrostatic discharge:

- 1. The operator shall ground through the anti-static wristband.

- 2. The equipment shell must be grounded.

- 3. The tools used in the assembly process must be grounded.

- 4. Must use conductor packaging or anti-static materials packaging or transportation.

+86-571-89966911

Rm701, No.9 Building, No. 1 WeiYe Road, Puyan Street, Binjiang District, Hangzhou, Zhejiang

VERSION: V1.1

http://www.relmon.com